Product Summary

The GAL26CV12B-20LP at 7.5ns maximum propagation delay time, combines a high performance CMOS process with Electrically Erasable (E2) floating gate technology to provide the highest performance 28-pin PLD available on the market. E2 technology of GAL26CV12B-20LP offers high speed (<100ms) erase times, providing the ability to reprogram or reconfigure the device quickly and efficiently.

Parametrics

GAL26CV12B-20LP absolute maximum ratings: (1)Supply voltage VCC: –0.5 to +7V; (2)Input voltage applied: –2.5 to VCC +1.0V; (3)Off-state output voltage applied: –2.5 to VCC +1.0V; (4)Storage Temperature: –65 to 150℃; (5)Ambient Temperature with Power Applied: –55 to 125℃.

Features

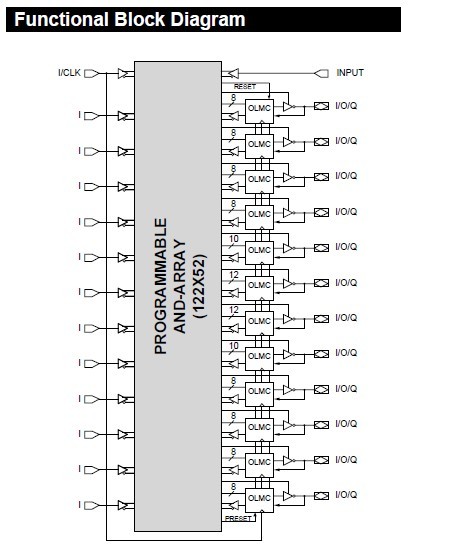

GAL26CV12B-20LP features: (1)high performance E2CMOS technology; (2)active pull-ups on all pins; (3)low power cmos; (4)E2 cell technology; (5)twelve output logic macrocells; (6)preload and power-on reset of registers; (7)electronic signature for identification.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

GAL26CV12B-20LP |

Lattice |

SPLD - Simple Programmable Logic Devices HI PERF E2CMOS PLD |

Data Sheet |

Negotiable |

|

||||

|

GAL26CV12B-20LPI |

Lattice |

SPLD - Simple Programmable Logic Devices HI PERF E2CMOS PLD |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))